IntelがXe-LP採用のデータセンター向けGPUの情報を公開した。

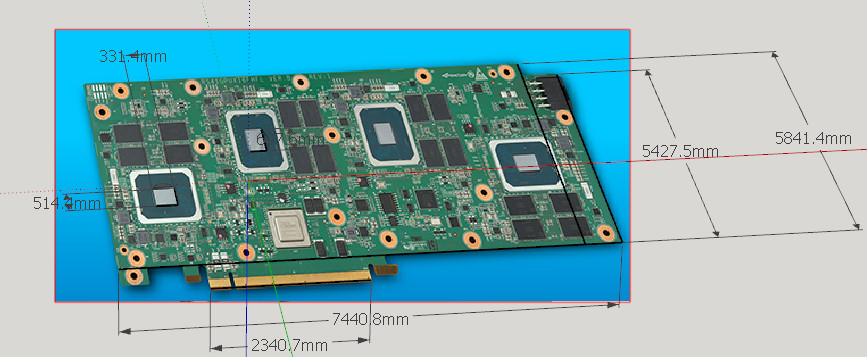

ここに基板の画像やボードの外観があったので、そこからXe-LPのダイサイズを推定してみる。

基板の画像は斜めからのものになっており、かつ縮尺もなんか怪しい。そこで、まずはボードの外観からボードの縦横比を調べ、これに基づき基板画像の縦横比を補正する。

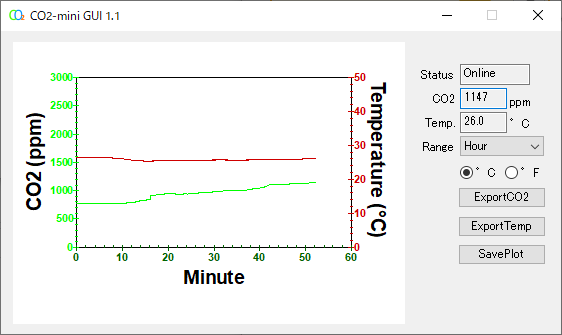

まずはボードの外観。比を取るため、単位は無視で。

幅89mmのPCIe x16コネクタ幅が2387なので、これを基準とすることで各部の寸法が求まる。すなわちコネクタ部を無視すると、基板のサイズは幅282.5mm、高さ104mmである。

次に、基板のほうを投影の補正をかけつつ比をとってみる。

こちらもPCIe x16コネクタサイズから基板のサイズを推定してみると、幅283mm、高さ222mmとなった。幅はほぼ一致したが、高さが合わない。どうも、基板の縦横比をいじっているようだ。ボード外観を正とすると、高さは本来の2.135倍されているようだ。

以上より、ダイの寸法を求める準備ができた。まず、一番左のダイだが、幅12.6mm、高さ9.2mm。

検算のため、向きの異なる左から3番目のダイでも高さと幅を求めると、高さ12.1mm、幅9.3mmとよく一致した。

以上より、Xe-LP用のダイサイズはおよそ12.4mm×9.2mmほどと思われる。

北森瓦版 177064氏より、メモリチップサイズを基準にした場合と寸法が異なる、またPCIeコネクタサイズも違うと指摘されたので確認してみる。

まず、PCIeコネクタのサイズから。手元基板を実測したところ、84mmであり177064氏が正しかった。自分が参照したのは、端子サイズではなくコネクタサイズだったようだorz

次に、縦横比について。横長のメモリチップの横幅は400.7、一方縦長のメモリチップの縦幅は824.5。両者が同一チップだとすると、高さは本来の2.06倍されていることになる。

以上から一番左のダイサイズを推定してみると、11.9mm ×9.0mm。同様に左から3番目のダイサイズを推定してみると、11.9mm × 8.8mm。元画像ではダイの画像が15~20ドット程度しかないので、この程度の違いは誤差。平均値をとって、11.9mm × 8.9mm程度と思われます。